# Silicon photonic terabit/s network-on-chip for datacenter interconnection

Chong Zhang, John E. Bowers\*

Department of Electrical & Computer Engineering, University of California Santa Barbara, Santa Barbara, CA, USA 93106 \*bowers@ece.ucsb.edu

#### **ABSTRACT**

Silicon photonic integration is an enabling technology for power- and cost-effective optical interconnects in exascale performance computers and datacenters which require extremely low power consumption and dense integration for a higher interface bandwidth density. In this paper, we experimentally demonstrate a fully integrated optical transceiver network on a silicon substrate using heterogeneous integration. High performance on-chip lasers, modulators and photodetectors are enabled by transferring III-V materials to a pre-patterned silicon substrate. Wavelength division multiplexed transceivers with eight wavelength channels are monolithically-integrated on a single chip, forming an optical network-on-chip circuit with total transmission capacity up to 8×8×40 Gbps, and bandwidth density over 2 Tbps/cm. We show that the heterogeneous silicon integration provides the design flexibility and scalability for high-speed optical communication systems.

## **Keywords**

Heterogeneous silicon integration; Network on chip; Optical interconnection.

#### 1. Introduction

The demand of fast, reliable, and low-cost optical data links has led to research in developing the next generation of photonic integrated circuits (PICs) to improve the power efficiency, latency, and capacity. In past decade, the power required for photonic transmission in data centers and supercomputers has been dramatically reduced in energy per bit. The transmitter size per capacity has been reduced by a factor of 10-100, and in the same time the bandwidth capacity has been increased from 10 Gb/s to 400 Gb/s in short links. However, the typical energy consumption of 10-100 pJ/bit to date must shrink further by another 2 to 3 orders of magnitude within the next few years for practical optical interconnection applications [1, 2]. This demand can be achieved with complete integration with a high bandwidth density, low power module, and most importantly a low-cost package technique.

Silicon photonics has shown its great potential for monolithic integration with the well-developed complementary metal—oxide-semiconductor (CMOS) fabrication [3-7]. Benefiting from the low loss of Si and advanced process techniques, a variety of functional components, including low loss waveguides (WGs) [8-9], modulators [10-12] and photodetectors [13-15] have been developed on the silicon-on-insulator (SOI) platform. Monolithic integration of photonic components with the electrical driver and/or other logic circuits were demonstrated on silicon with a standard semiconductor foundry process [16-18]. As an example, reference [18] presented the first single-chip microprocessor with embedded optical interconnection between processor core and memory bank with on-chip modulators, photodetectors and off-chip light source. Such approach requires co-design and co-process of optical and electrical components, and in many cases compromises must be made between the two parts of the system. Therefore, it is better to optimize and fabricate the photonic chips and driver circuits individually, and then integrate both circuits together with 2.5D or 3D architecture in a compact chip package [19, 20]. Advanced signal multiplexing techniques are normally involved in the photonic circuit design to scale up the chip bandwidth. In particular, integrated wavelength division multiplexing (WDM) systems combined with single mode fiber shows great advantages compared with discrete links such as vertical cavity surface emitting laser (VCSEL) links in short distance communication [21-23].

However, the lack of a reliable silicon laser has been the major impediment due to the fundamental material limit of silicon, which has an indirect band-gap. Three approaches have been widely used to achieve an on-chip laser by introducing efficient light emission materials on silicon with three major approaches: (1) hybrid, (2) heteroepitaxy or (3) heterogeneous integration. The hybrid assembly approach couples the laser output from a III-V chip with gain section into the silicon chip laterally [24, 25] or vertically [20, 26]. This approach allows optimization and fabrication of the III-V and silicon chips individually, but it is mainly limited by the complications in light coupling and device packaging, as well as the extra fabrication cost of two separate chip fabrication. Direct epitaxial growth of III-V materials, especially quantum-dot (QDs) gain materials on silicon is a promising solution for high performance lasers with high volume throughput [27-31]. However, the lifetime and reliability of the heteroepitaxial lasers requires further improvement. Moreover, heteroepitaxial growth normally has a thick or dedicated buffer layer to annihilate the propagating dislocations from the heterogeneous interface, which makes it difficult to couple the laser output into the waveguide at the silicon layer. In this paper, we focus on the heterogeneous silicon integration (HSI) approach, which transfers the functional materials to silicon with a wafer bonding technique [32-37]. By using a selective die bonding method, which selectively places a number of small III-V chips to designated zones on a large silicon wafer, the total cost can be dramatically reduced, and multiple functionality can be realized by integrating different epitaxial structures on the single chip [38]. This platform is not limited to the integration of III-V materials, but can be

applied to a wide variety of material systems to integrate nonlinear and nonreciprocal materials for many different applications [39-42].

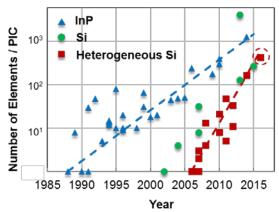

**Fig. 1.** Evolution of photonic integration in terms of number of devices on a single waveguide on chip. Silicon photonic (green circle) represents the "passive" integration without an on-chip laser; InP integration (blue triangle) and heterogeneous silicon integration (red square) have integrated active devices including lasers on-chip. The circled data point indicates the PIC reported in this work.

Fig. 1 shows the evolution of InP- and silicon- based photonic integration platform in terms of number of devices integrated on one chip, representing "Moore's Law" in the photonic integration field. With more and more photonic devices integrated on the single chip, both the complexity and functionalities of the PICs have been greatly improved in past three decades. Silicon photonic integration is catching up with InP-based III-V photonic integration. Benefitting from the compact component footprint and low loss waveguide, over 4000 devices were integrated in the large-scale silicon phase tuning array chip in 2013 [43]. Particularly, with an efficient on-chip laser solution, the HSI platform has been rapidly growing since its invention in 2006. This paper will summarize the design and demonstration of our recent advances on heterogeneous integrated optical network-on-chip (ONoC) circuit [44]. With eight transceiver nodes and over 400 photonic components in a single die, large communication capacity was achieved for the application of high-speed datacom interconnects in high performance computers (HPCs) and data centers. The remainder of this paper is organized as follows: Section 2 shows the architecture of the ring optical network. Section 3 discusses the photonic circuit design and fabrication process. Section 4 and 5 report the characterization of key components and the optical network circuit, respectively. Finally, section 6 summarizes this paper.

## 2. ONoC architecture

The ONoC topology defines the structure of the network and controls how data flows among the transceiver nodes in the network. A number of ONoC topologies have been reported [45-49], such as Corona [45], Firefly [46], ATAC [47], etc., typically designed for a multi-core system with 2-D or 3-D photonic integration. In the case of the Corona network, the WDM clusters are connected to bus waveguide with resonator structures [45]. As a wavelength-selective switch (WSS) component, the microring resonator picks up one channel of the WDM spectrum as either modulator/multiplexer (Mux) or photodetector/demultiplexer (DeMux). However, the bandwidth at each node is limited by the modulation speed and the optical bandwidth of the microrings.

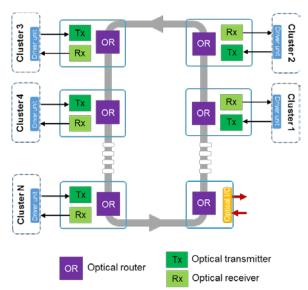

In this paper, to overcome this bandwidth limit, we propose a ring network architecture based on broadband optical switches instead of WSS components. The network architecture has a ring topology with circular and close bus waveguide as the basis infrastructure, as schematically shown in Fig. 2. Multi-nodes of photonic WDM transceivers are attached to the bus through broadband optical routers/switches. The transmitter/receiver nodes have individual electrical/optical (E/O) interface to CMOS driver and the corresponding clusters. Two spare nodes in this chip are present with optical interface for coupling with single mode fibers. The broadband optical routers/switches control all the WDM channels simultaneously to scale up the total bandwidth at each node.

Such ring architecture defines a reconfigurable network that can be controlled by varying the working status of the optical routers, as illustrated in Fig. 3. With a normally-off switch design, the default mode is at self-communication or self-configuration status, where the transmitter is talking to its local receiver for self-testing or initialization (Fig. 3(a)). By fully turning on any two of the switches in the network, all WDM channels at one transmitter or from the off-chip optical interface can be routed to another node simultaneously, as a cluster-to-cluster or point-to-point mode (Fig. 3(b)). It can also work at a broadcasting mode as a 1×N network by partially turning on the switch array (Fig. 3(c)). This reconfigurable network architecture provides flexibility in system designs based on practical applications. It is to note that, all transceiver nodes share identical WDM channels, thus traffic conflicts need to be avoided by carefully controlling the switch array. The data stream can only flow in one direction on the bus waveguide, due to the directionality of the light coupling in the optical switches. There are two ways to scale up the number of clusters in this network: more clusters can be added to one bus loop considering a low insertion loss from the bus waveguide and switch bank; two or more bus loops can be cascaded through the optical input/output (I/O) ports to form a multi-ring architecture.

Fig. 2. Architecture overview of the ONoC circuit.

Fig. 3. Reconfiguration modes of ring network: (a) self-configuration, (b) cluster to cluster and (c) broadcasting mode.

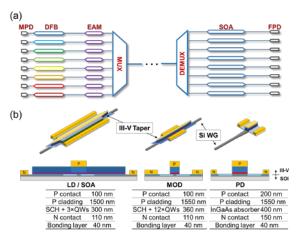

## 3. Heterogeneous silicon integration

Most of the key elements for an on-off keying (OOK) optical link are available on the heterogeneous silicon integration platform, including low threshold current distributed feedback (DFB) lasers, high-speed Mach-Zehnder modulators and electroabsorption modulators (EAMs), high power semiconductor optical amplifiers (SOAs) and high-speed photodetectors (PDs) [50-55]. Fig. 4(a) schematically shows the layout of the WDM transceiver. The transmitter has 8 wavelength channels in the C/L band with 200 GHz spacing. Each channel has a continuous-wave (CW) DFB lasers as the single-color light source, a high-speed EAM for intensity modulation, and a monitoring PD (MPD) to in-situ monitor the laser output power and to provide feedback control. The corresponding 8-channel receiver has fast PDs (FPDs) with P-I-N structure and InGaAs absorptive layer. Part of the receivers consist of SOAs with same gain materials as the laser to amplify the received optical power and compensate any high optical loss from fiber coupling or transmission in long waveguide. 1×8 silicon array waveguide grating (AWG) are adopted as symmetric Mux/DeMux. The data upstream and downstream are controlled by a Mach-Zehnder interferometer (MZI) switch which covers the broad spectrum over 1.6 THz (8×200 GHz). Fig. 4(b) shows the schematic and cross-sections structure of the heterogeneously integrated devices used in the transceivers. All the device epitaxial layer structures are carefully designed, so that they are compatible with same device fabrication. The DFB/SOA/MPD epi consists of 3 InAlGaAs quantum wells (QWs) with photoluminescence (PL) center wavelength at 1545 nm; the EAM epi has 12 InAlGaAs QWs with PL wavelength at 1485 nm; the FPD epi has 400 nm InGaAs bulk layer as the light absorber.

They share the same contact layers: InP for n-type contact and InGaAs for p type contact, so same contact metallization can be applied with one deposition. The same InP bonding interface with super lattice (SLs) are used for the selective bonding process.

On the other hand, those different types of devices structures are optimized individually. Lasers and SOAs have wide mesas with 4  $\mu$ m wide current channel defined by H<sup>+</sup> implant. Lasers have a 400  $\mu$ m long cavity and SOAs have 1.5 mm. A short (20  $\mu$ m) taper is used to couple the light from silicon waveguide to III-V/Si heterogeneous waveguide. EAMs have a narrower mesa defined by dry etch to reduce parasitic capacitance, and a longer taper (60  $\mu$ m) for low insertion loss. The PDs also have a compact mesa design for low capacitance, but wider mesa and silicon waveguide to improve the responsivity. Instead of heterogeneous tapers, PDs have adiabatic silicon tapers at input and 7° slanted III-V interface to eliminate unnecessary reflections back to the input waveguide.

**Fig. 4.** (a) The WDM transceiver architecture in the ONoC circuit, and (b) the device structure, cross-sections and epi stack of the heterogeneous laser /amplifier, modulator, and photodetectors, respectively.

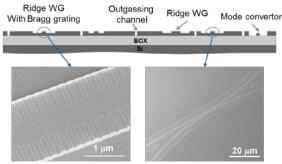

The ONoC circuit fabrication has two major parts: silicon (passive) process and III-V (active) process. The silicon process defines the grating, waveguide, (De)Mux, switch and all other silicon components on the silicon-on-insulator (SOI) substrate with 500 nm thick device layer and 1  $\mu$ m buried oxide (BOX) layer. As the first step, first-order Bragg grating sections in DFB cavities were defined with a JEOL JBX-6300FS E-beam lithography (EBL) system and etched with a reactive ion etching (RIE) tool. The Bragg grating pitches were finely tuned to control the wavelengths to the eight WDM channels. A quarter-wavelength phase-shifted section was at the center of the laser cavity. Waveguides, including ridge waveguide (partially etched), stripe waveguide (fully etched) as well as outgassing channels (fully etched) were patterned with an ASML 248-nm deep-ultraviolet (DUV) lithographic stepper. Fig. 5 shows the cross-sectional diagram of the SOI substrate after the passive process, and scanning electron microscope (SEM) images of the Bragg gratings on silicon waveguide and directional coupler with ridge waveguide. The etch depth of grating and ridge waveguide are 30 nm and 200 nm, respectively. Multimode (2  $\mu$ m) ridge waveguides are used between transceiver nodes for low propagation loss, and they adiabatically taper down to single mode (600 nm) waveguide at bending to avoid large leakage.

Fig. 5. Diagram of SOI substrate after process, and the SEM images of Bragg gratings on silicon ridge WG and directional coupler.

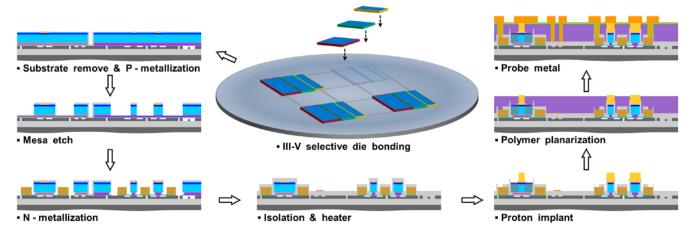

The III-V processes were performed after the selective die bonding, as shown in Fig. 6. After thorough clean and oxygen plasma treatment on both III-V chip and SOI, the bonding process was operated in a Finetech pick-and-place tool with below 10- $\mu$ m precision. The gap between III-V bonded samples was controlled below 100  $\mu$ m, and then a thin layer of silicon dioxide was deposited to protect the exposed silicon waveguide inside the gaps. After III-V substrate removal, the mesas of laser/modulator/photodetector were etched with Methane/H<sub>2</sub>/Ar RIE etch, followed by selective wet-etch to expose the bottom n-InP contact layer. A thick silicon dioxide layer was deposited after n-type metallization. After Ti/Pt heater/tuner and p-type metallization, the sample was implanted with protons to define the 4  $\mu$ m current channel in the laser and SOAs, as well as to isolate the EAM cavity with the long tapers. Pd/Ti/Pd/Au and Pd/Ge/Pd/Au metal stacks were used as p- and n- type contacts, respectively. The sample was planarized with 3  $\mu$ m polymer (Benzocyclobutene, or BCB used in this work) before final metallization to further reduce the parasitic capacitance from the substrate.

Fig. 6. Schematic of selective die bonding on SOI and fabrication steps of III-V/Si after bonding.

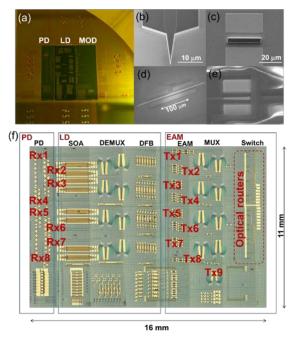

Fig. 7(a) shows a microscope image of the photonic chip after III-V bonding. A 100-mm diameter SOI wafer was used due to the tool limit. Three pieces of III-V epi bonded in parallel in each quarter, covering a whole die with about 19×19 mm². The transceiver circuit locates in the middle of the die, with a size about 11×16 mm². Fig. 7(b-d) shows SEM images of the heterogeneous laser, photodetector and modulator after mesa etch and metallization. Because of the good resolution of DUV lithography, sharp adiabatic III-V tapers with 300 nm tip width were achieved, which is preferred for low transition loss and low power reflection. Fig. 7(e) shows the opened via on modulator mesa and n-metal after BCB planarization. Over 400 functional photonic components, including both passive and active devices, were interconnected with silicon waveguide into an integrated network system, as shown in the stitching microscope image in Fig. 7(f). The footprint of each transmitter or receiver node is roughly 1×6 mm², mainly limited by the size of the AWGs. The switch array is located at the right side of the chip, highlighted by the red dash box, with metal pads compatible with a 16-pin probe card. The blue boxes in Fig. 7(f) indicate the bonding positions of III-V epi. After the process the chip was diced into dies with facets polished for fiber coupling and characterization. The process yield of the individual photonic components was evaluated by testing the monitoring devices. The process yield of passive components was 100%, and the overall yield was about 90% counting both active and passive elements. The high yield was benefitting from a series of tolerant device designs, such as wavelength-insensitive and broad band designs; the failed devices was mainly due to process imperfections, such as bonding defects that resulted from the imperfect process environment.

**Fig. 7.** (a) Microscope image of the photonic chip after multiple die bonding and device mesa etch; and SEM images of (b) laser mesa with 20 μm taper; (c) FPD mesa with n-contact metal; (d) EAM after mesa etch with 100 μm cavity and 60 μm tapers; (e) deep via in the thick polymer after surface planarization; (f) microscope image of the photonic transceiver circuit.

## 4. Device design and performance

## 4.1 Broadband optical switch

A broadband optical router and switch is of great interest in an alignment-free optical network or WDM system. Microelectromechanical based optical switches are normally broadband, but their large footprint make it difficult to be integrated on chip [56]; Resonator based switches have small size, but they normally have narrow bandwidth [57,58]. Broadband optical switches are reported with multimode interference coupler or broadband 3-dB couplers based MZI switches [59, 60]. However, they are normally very sensitive to fabrication variations. In this work, we propose a novel adiabatic coupler MZI (ACMZI) switch, which adopts the adiabatic coupler as the 3-dB power combiner/splitter in a MZI structure, so that the switch can work for a wide wavelength range.

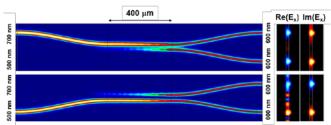

In an adiabatic coupler, the two unbalanced arms are brought close gradually to avoid abrupt mode perturbation, and then change the waveguide width slowly enough with a constant gap width. During this transition the fundamental mode on each arm will adiabatically change to an even/odd mode and then optical power is evenly split to two symmetric outputs [61]. In this design, the input ridge waveguide widths are chosen to be 700 nm and 500 nm, while the output waveguide is 600 nm. The coupling gap is 300 nm. Fig. 8 shows the simulated light propagation with fundamental transverse electric (TE) mode at 1550 nm wavelength. It can be seen that an even mode is activated when the light inputs from the wider arm, and odd mode is activated when the light inputs from the narrow arm, both resulting in an even power split.

Fig. 8. Simulations of light propagation in an adiabatic coupler

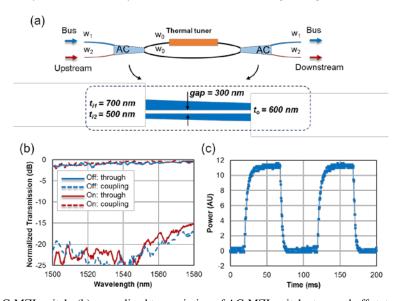

Fig. 9(a) shows the structure of the MZI switch with adiabatic couplers [62]. Two 3-dB adiabatic couplers are connected back to back to form a symmetric interferometer structure. A thermal phase tuner on one arm is to change the phase difference between two arms and to control the power split ratio. As introduced in the process section, the ridge waveguide was partially etched with 200 nm ridge height and 300 nm slab thickness. 1  $\mu$ m SiO<sub>2</sub> layer was deposited on the coupler, isolating the silicon waveguide from the top Ti/Pt heater metal. 2  $\mu$ m wide deep trenches were etched on both sides of the waveguide to improve the thermal efficiency of the phase tuner. The performance of AC-MZI switch is shown in Fig. 9(b). It shows an on-off extinction ratio (ER) larger than 16 dB across over 80 nm wavelength range on both coupling and through ports. Fig. 9(c) shows the tuning response of the AC-MZI switch in time domain under a square wave signal on the phase tuner. It has about 18 ms rise time which corresponds to a 30-kHz bandwidth, which is fundamentally limited by the low efficiency of the indirect thermal tuning through a thick oxide spacer layer.

**Fig. 9.** (a) Structure of the AC-MZI switch; (b) normalized transmission of AC-MZI switch at on and off status; and (c) its response to a 10-kHz square wave voltage driving on the phase tuner.

4.2 (De)Mux

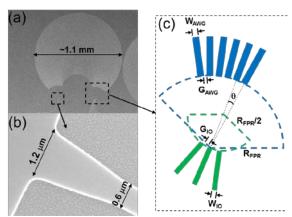

AWGs are widely used as the (De)Mux in a WDM system due to their dense channel spacing, low cross talk and compatibility to integrated circuits [63-65]. A symmetric AWG design is used in this work, as the SEM images show in Fig. 10(a). It consists of three major parts: I/O waveguides, star-couplers with free propagation region (FPR), and the phase waveguide array. Fig. 10(c) labels the parameters used in this work, with the design values listed in Table 1. The array waveguide width is set to be 1.2  $\mu$ m, which is slightly multimode, for low loss and low crosstalk [66]. The 1×8 AWG has a footprint about 1.2 mm<sup>2</sup>. A parabolic taper is used at the I/O waveguide to improve the channel uniformity, as shown in Fig. 10(b) [67]. In order to reduce the total insertion loss of the large component, all the waveguides are partially etched; minimum 200  $\mu$ m bend radii was used for low leakage loss; the gap between neighboring array waveguides was 200 nm, limited by the lithographic resolution.

Fig. 10. SEM images of the (a)AWG design and (b) the I/O waveguide with parabolic taper; (c) the AWG design used in this work.

| <b>Table. 1.</b> Design parameters of the 1×8 AWG |                             |            |

|---------------------------------------------------|-----------------------------|------------|

| Array WG                                          | $N_{AWG}$                   | 127        |

|                                                   | $\Delta L$                  | 17.471 μm  |

|                                                   | $\mathbf{W}_{\mathrm{AWG}}$ | 1.2 μm     |

|                                                   | $G_{ m AWG}$                | 200 nm     |

| FPR                                               | $R_{FPR}$                   | 159.035 μm |

|                                                   | $N_{IO}$                    | 1×8        |

|                                                   | $W_{IO}$                    | 1.2 μm     |

| I/O WG                                            | $G_{IO}$                    | 1.2 μm     |

|                                                   | Taper_L                     | 2 μm       |

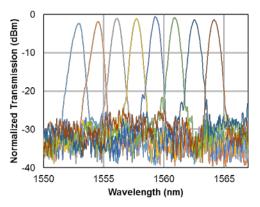

The normalized transmission spectrum of the  $1\times8$  AWG is shown in Fig. 11. A low insertion loss was achieved below 1.5 dB at the center channel, and the non-uniformity among the eight channels is about 1 dB. The channel crosstalk was as low as -28 dB. The average optical bandwidth of single channel is 0.62 nm, or 75 GHz in the frequency domain.

**Fig. 11.** Normalized transmission spectrum of the  $1\times8$  AWG.

## 4.3 Heterogeneous DFB laser

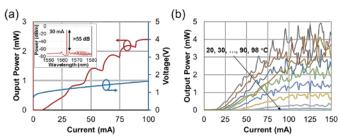

The heterogeneous DFB laser was used as the laser source due to its low threshold current and single mode operation. In this work, the laser cavity length is 400  $\mu$ m, which is longer than previous work to improve the device thermal impedance and series resistance [50]. The epitaxial layer design with 3 QWs is for lower transparency current density and lower threshold current density. A weak Bragg grating is required for such a long cavity. For this purpose, an edge Bragg grating was used instead of etched grating across the whole waveguide. The etched corrugations are defined at the edge of the waveguide, as shown in Fig. 5. The grating width  $W_g$ , is a new degree of freedom in design to finely tune the overlap between the grating tooth with guided optical field. Here, we used 30 nm

grating etch-depth and 400 nm grating width on the 1  $\mu$ m silicon waveguide. The quarter-wavelength shifted Bragg gratings is carefully aligned with the silicon waveguide layer, which is critical to achieved desired grating strength and center wavelength.

Fig. 12. (a) L-I-V curves of 400 μm heterogeneous DFB laser. Inset is the lasing spectrum at 30 mA current injection. (b) The CW operation of a 400 μm long heterogeneous DFB laser at high stage temperature up to 98 °C.

Fig. 12(a) shows light-current-voltage (L-I-V) characteristics of the heterogeneous DFB laser with 400  $\mu$ m cavity under CW operation. The threshold current was measured to be 7.5 mA, corresponding to a threshold current density of 470 A/cm² at 20 °C. This shows an over 50% improvement compared with the previous 200  $\mu$ m cavity DFB with 7-QWs [50]. The inset lasing spectrum in Fig. 12(a) indicates a single wavelength emission with a side mode suppression ratio (SMSR) over 55 dB. The kinks at the L-I curves relate to longitude mode hopping. This DFB laser on silicon kept CW lasing at high ambient temperature up to 98 °C, as shown in Fig. 12(b).

## 4.4 Heterogeneous EAM

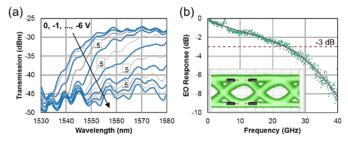

Electroabsorption modulated lasers (EMLs) are widely utilized in commercial optical transponders, with their advance in broadband, small footprint, large extinction ratio and high-speed modulation [68-70]. With a strong quantum confined Stark effect, the III-V quantum-wells structures can manipulate the absorption edge with the external electric filed. EAMs with lumped electrodes are used in this photonic circuit design [52]. Similar to integrated lasers we just discussed, the EAMs have a heterogeneous III-V/Si waveguide as the absorptive section between the adiabatic tapers, as shown in Fig. 4(b). However, the III-V epi consists of a thick active region with 12 QWs. 2.5 μm mesa width and 750 nm Si waveguide width are used to enhance the mode confinement factor in the QWs. The absorptive section is 75 or 100 μm long, which is a tradeoff between insertion loss and modulation depth.

Fig. 13(a) shows the transmission performance of the 100  $\mu$ m long EAM at varying reverse bias from 0 to 6 V. The optical input is at TE polarization. Over 6 dB per 1 Vpp extinction ratio can be achieved across 1550-1570 nm with a low DC bias voltage below 3 V. The small signal frequency response of the heterogeneous EAM was measured in a lightwave component analyzer (LCA), as the result shown in Fig. 13(b). Over 24 GHz bandwidth is achieved on the EAM with a 75×2.5  $\mu$ m<sup>2</sup> cavity. The inset shows a clear open eye diagram at 25 Gbps operation.

Fig. 13. (a) Power transmission of  $100\times2.5~\mu\text{m}^2$  EAM versus reverse bias from 0 to 6 V (0.5 V interval); (b) EO response of EAM with 75  $\mu$ m cavity and 2.5  $\mu$ m mesa width at 1560 nm wavelength and 2V reverse bias. Inset: eye diagram under 25 Gbps operation with 1560 nm input wavelength and 3.3 V reverse bias.

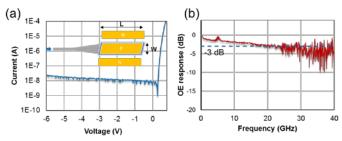

## 4.5 Heterogeneous photodetector

The photodetector is another critical component in the transceiver network. A waveguide photodetector is used in this design, with a vertical PIN structure and 400 nm InGaAs intrinsic layer as the absorber [71, 72]. The input silicon waveguide is flared out to multimode waveguide with the same width of the III-V mesa. The PD cavity has a 4  $\mu$ m wide and 30  $\mu$ m long, as shown in the inset of Fig. 14(a). A low dark current of 10 nA at 2 V reverse voltage was achieved, shown in Fig. 14(a), benefitting from the optimized mesa dry etch and sidewall passivation process. The OE frequency response of the heterogeneous PD in Fig. 14(b) shows 3-dB bandwidth of 20 GHz. The internal responsivity of the photodetectors is measured at 1550 nm wavelength with TE polarization. The responsivity of the photodetectors with  $30\times4~\mu\text{m}^2$  mesa was 0.45, and a higher responsivity can be achieved with a longer/wider cavity. The efficiency of the waveguide photodetectors can be improved with further mode engineering, such as to squeeze the mode into the absorber layer by tapering down the silicon waveguide.

Fig. 14. (a) I-V curve of heterogeneous PD with  $4\times30~\mu\text{m}^2$  and its top-view diagram in inset, and (b) its normalized small signal frequency response.

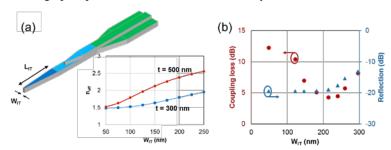

## 4.6 Inverse taper for fiber coupling

Coupling loss between silicon waveguide and optical fiber is one of the major sources of total optical loss in an optical link. Vertical fiber coupling with a grating coupler (GC) has coupling loss as low as 1.5 dB per coupling with dedicated multi-level designs [73, 74]. However, a low reflection and low loss GC design is still missing for the 500 nm SOI platform. Instead, edge butt coupling is commonly used, suffering from difficult alignment due to the large mode mismatch between waveguide and fibers. Other optimizing techniques, such as a waveguide mode convertor design [75-77], are not compatible with the thick device layer. To solve this problem, we designed a three-sectional mode convertor for a low loss fiber coupling. As shown in Fig. 15(a), the mode converter consists of three sections: (a) transition from partially-etched ridge waveguide to fully-etched stripe waveguide, (b) transition from stripe waveguide with 500 nm height to 300 nm height, and (c) an inverse taper with 300 nm height. This 300 nm tall strip waveguide is necessary for the inverse taper to "squeeze" the TE mode into the SiO<sub>2</sub> cladding at the taper tip, to achieve a low effective index and better overlap with fiber mode, as shown in the inset in Fig. 15(a). Therefore, neither extreme narrow taper tip nor EBL process is required in the process. In this work, 150 to 200 nm inverse taper tip widths were achieved with DUV lithography. The inverse taper 8-degree tilted from the normal direction from the facet to reduce the reflection. Fig. 15(b) shows experimental results of coupling efficiency and reflection with different inverse taper length and tip width. The minimum coupling loss was 4.7 dB per coupling when the taper tip width was 225 nm. The minimum reflection is about -20 dB at a taper tip width of 200 nm. The coupling loss can be further reduced with improved lithographic process and with a thicker BOX layer in the SOI substrate.

Fig. 15. (a) Diagram of the mode convertor on 500 nm SOI. Inset shows the effective index of the inverse taper changing with waveguide width; (b) measured fiber coupling loss and power reflection with the mode convertor.

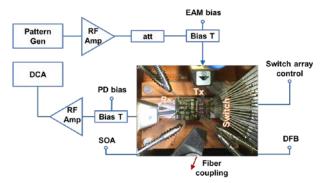

## 5. On-chip interconnection

The diagram in Fig. 16 shows the setup for on-chip communication with the heterogeneously integrated ONoC circuit. Due to lack of an appropriate driver circuit, only one channel was tested at a time. The switch array was driven by a multi-pin probecard to route the data flow among transceivers. GSG radio frequency (RF) probes with  $50~\Omega$  impedance are used to directly drive the modulators and photodetectors, and needle probes are for DC bias of laser, SOA, monitor PD, etc. Broadband RF power amplifiers are used to boost the RF signal on modulator and the received signal from PD, and high-speed bias-tees to provide DC reverse bias on the modulator and PD. Small signal measurements are performed in a 67 GHz LCA, and the optical data transmission tests are performed with a high-speed digital communication analyzer (DCA). A 40 Gbps RF pattern generator is to provide pseudorandom binary sequence (PRBS) signal as the input signal. The DCA and pattern generator are synchronized with a frequency generator as the clock signal. Single mode fiber with 2  $\mu$ m lensed tip is aligned with the silicon inverse taper at the facet for optical I/O coupling.

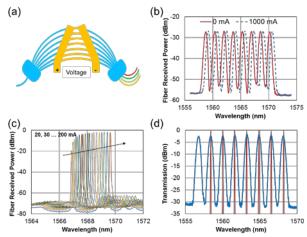

All the eight WDM channels of the AWG can be tuned simultaneously by the differential heater array on the array waveguides, as shown in Fig. 17(a) and (b). However, this tuning method is power intensive with an efficiency of 50 GHz/W, which is due to the inefficient thermal tuner design in this work. An alternative approach to align the laser wavelength with the AWG channel is to change the laser wavelength by adjusting the injection current, as shown in Fig. 17(c). With increasing the injection current from 20 mA to 200 mA, the lasing wavelength continuously scans over 3 nm. With manually tuning the wavelength of laser and AWG appropriately, eight DFB lasers with wavelength aligned to the corresponding AWG channels are shown in Fig. 17(d). The missing channel was caused by a defective device on the chip. The normalized transmission spectrum in Fig. 17(b) and (d) is from two back-to-back 1×8 AWGs on one waveguide, representing an ultra-low total insertion loss below 3 dB through two AWGs in transmitters and receivers.

Fig. 16. Testing setup of the chip-level communication of the ONoC circuit.

Fig. 17. (a) Schematic diagram of AWG with differential thermal tuner; (b) transmission spectrum of two cascaded back to back AWGs before and after thermal tuning; (c) output spectrum of  $400~\mu m$  DFB laser with different injection current levels; and (d) the normalized wavelength of laser array aligned with the AWG channels.

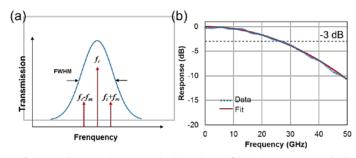

It's worth noting that the RF signal with high speed data degenerates after the AWG. Due to the optical spectrum filtering effect, as illustrated in Fig. 18(a), when a non-return-to-zero (NRZ) signal with carrier frequency ( $f_c$ ) and modulation frequency ( $f_m$ ) passes a AWG channel with narrow optical bandwidth, both sidebands of the NRZ signal are truncated by the Gaussian-like optical filter, so that its response at higher frequency is depressed at the same time. With the AWG transmission shown in Fig. 11, its optical spectrum filtering effect has a 3-dB bandwidth of 26.5 GHz, as shown in Fig. 18(b). Consequently, at zero-detuning working status, a data-rate dependent power penalty of 0.25 dB and 0.52 dB for 25 Gbps and 50 Gbps data rate, respectively, can be expected [78].

**Fig. 18.** (a) Spectrum filtering effect of an AWG channel as an optical band pass filter, the red arrows indicating the NRZ modulation signal; (b) calculated frequency response of an AWG optical channel.

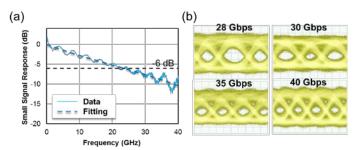

The small signal frequency response of the modulator with corresponding photodetector in the receiver is shown in Fig. 19(a). A 6-dB bandwidth of 24 GHz was observed in the EAM-PD link. RF power reflections are seen due to the impedance mismatch between the 50  $\Omega$  probes and the high-impedance devices under reverse bias. The data transmission test with  $2^7$ -1 PRBS signal with the setup shown is shown in Fig. 16. A data rate up to 40 Gbps per channel performance is shown in Fig. 19(b), with the vertical scale of 50 mV/div in the eye diagrams. The unsymmetrical eye patterns are due to the clock distortion from the pattern generator. Clear eyes can be seen up to 40 Gbps operation, which is limited by the microwave amplifiers. The result shows a potential ultra-large capacity of the transceiver network, with 320 (8×40) Gbps per transceiver node, and 2.56 Tbps (8×320 Gbps) for the whole photonic circuit.

Further improvements are expected with integration of the photonic transceiver circuit with impedance matched CMOS driver circuit for low bit error rate operations.

Fig. 19. (a) Small signal frequency response of the on-chip WDM channel; (b) Eye diagrams of on-chip communication from one WDM channel with varying data rate.

In this demonstration of on-chip interconnections, the photonic circuit's power consumption is dominated by the lasers. The DC power consumption of the DFB laser shown in the data link in Fig. 19(b) is about 1.5 pJ/bit with 70 mA current injection under a 40 Gbps data rate. A dynamic laser power tuning, with flexible laser control according to the link data rate, will be an effective way to save the energy consumption on the laser source. The power efficiency of laser wavelength tuning can be further reduced by incorporating a metal-oxide-semiconductor capacitor at the bonding interface [79]. The high-impedance modulator and photodetectors have about two orders of magnitudes lower power consumption compared with lasers. The total energy efficiency can be improved by integrating the photonic with electrical circuit to remove the 50  $\Omega$  transmission lines. However, the power that drains into the high-speed CMOS driver circuits is likely to take a large proportion of the total energy cost of a fully photonic-electronic integrated transceiver.

#### 6. Summary

In this paper, we propose and demonstrate a novel heterogeneously integrated ONoC circuit for high-speed optical interconnections over short distances. Over 400 photonic components, including 300 active devices were heterogeneously integrated onto a single die on silicon substrate. The WDM photonic transmitter network achieves 8×40 Gbps at each node, and 2.5 Tbps total capacity with a high bandwidth density over 2 Tbps/cm. This can be further scaled up, and the integration level is largely limited by the interface of the electrical driver for 2-D integration, e.g. with wire-bonding approach. We believe that the ultra-dense photonic integration that follows the photonic "Moore's Law" will dominate the future high-speed data transmission with 3-D integrations with electrical circuits, e.g. with flip-chip bonding approach or through silicon via approach [19, 20].

We have shown the capability of the heterogeneous integration to integrate different types of photonic devices on silicon, promising for future low-cost and large-bandwidth chip-level optical interconnects. Selective die bonding technology and design of heterogeneous III-V/Si waveguide play important roles in this newly developed platform. Fortunately, most design rules and fabrication techniques can be transplanted from the pure III-V and Si CMOS platforms. As the next step, reliable process design kits of heterogeneous integration circuit with co-design of electrical circuit are being developed, which will accelerate the application of this platform to large scale photonic integration in near future.

## **Funding**

This work is supported by Defense Advanced Research Projects Agency (DARPA) MTO POEM program (442530-22722).

## Acknowledgement

We thank Jon Peters, Shangjian Zhang, Clint Schow, MJ Kennedy, Jared Hulme, Geza Kurczveil, Jin-Wei Shi, Michael Davenport and Robert Zhang for useful discussions and help with fabrication and test. We thank UCSB nano-fabrication facility and staff for support.

## References

- [1] R. S. Tucker, Green optical communications Part I: Energy limitations in transport, IEEE Journ. of Sel. Topics in Quant. Electron., 17(2) (2011) 245-260

- [2] David A. B. Miller, Attojoule Optoelectronics for Low-Energy Information Processing and Communications a Tutorial Review, J. Lightw. Technol. 35(3) (2017) 346-396

- [3] Y. Arakawa, T. Nakamura, Silicon photonics for next generation system integration platform, IEEE Commun. Mag. 51(3) (2013) 72-77

- [4] R. Soref, The Past, Present, and Future of Silicon Photonics, IEEE J. Quantum Electron. 12(6) (2006) 1678 1687

- [5] Y. A. Vlasov, Silicon CMOS-integrated nano-photonics for computer and data communications beyond 100G, IEEE Commun. Mag. 50(2) (2012) s67-

- [6] A. E.-J. Lim, J. Song, Q. Fang, C. Li, X. Tu, N. Duan, K. K. Chen, R. P.-C. Tern, T.-Y. Liow, Review of Silicon Photonics Foundry Efforts, IEEE J. Quantum Electron. 20(4) (2014) 8300112

- [7] M. Asghari and A. V. Krishnamoorthy, Silicon photonics: Energy-efficient communication, Nat. Photon., 5(5), 268-270 (2011)

- [8] D. Dai, J. Bauters, J. E. Bowers, Passive technologies for future large-scale photonic integrated circuits on silicon: polarization handling, light non-reciprocity and loss reduction, Light Sci. Appl. 1(3) (2012) 1-12

- [9] S. K. Selvaraja, P. D. Heyn, G. Winroth, P. Ong, G. Lepage, C. Cailler, A. Rigny, K. K. Bourdelle, W. Bogaerts, D. V. Thourhout, J. V. Campenhout, P. Absil, Highly uniform and low-loss passive silicon photonics devices using a 300mm CMOS platform, Optical Fiber Communications Conference and Exhibition, (2014)

- [10] G. T. Reed, G. Mashanovich, F. Y. Gardes, D. J. Thomson, Silicon optical modulators, Nature Photon. 4 (2010) 518-526

- [11] Q. Xu, B. Schmidt, S. Pradhan, M. Lipson, Micrometre-scale silicon electro-optic modulator, Nature 435 (2005) 325-327

- [12] A. Liu, R. Jones, L. Liao, D. S.-Rubio, D. Rubin, O. Cohen, R. Nicolaescu, M. Paniccia, A high-speed silicon optical modulator based on a metal–oxide–semiconductor capacitor, Nature 427 (2004) 615-618

- [13] Y. Kang, H.-D. Liu, M. Morse, M. J. Paniccia, M. Zadka, S. Litski, G. Sarid, A. Pauchard, Y.-H. Kuo, H.-W. Chen, W. S. Zaoui, J. E. Bowers, A. Beling, D. C. McIntosh, X. Zheng, J. C. Campbell, Monolithic germanium/silicon avalanche photodiodes with 340 GHz gain–bandwidth product, Nature Photon. 3 (2009) 59 63

- [14] J. Michel, J. Liu, L. C. Kimerling, High-performance Ge-on-Si photodetectors, Nature Photon. 4 (2010) 527 534

- [15] P. Chaisakul, D. M.-Morini, J. Frigerio, D. Chrastina, M.-S. Rouifed, S. Cecchi, P. Crozat, G. Isella, L. Vivien, Integrated germanium optical interconnects on silicon substrates, Nature Photon. 8 (2014) 482–488

- [16] B. Analui, D. Guckenberger, D. Kucharski, A. Narasimha, A Fully Integrated 20-Gb/s Optoelectronic Transceiver Implemented in a Standard 0.13-μm CMOS SOI Technology, IEEE J. Solid-State Circuits 41(12) (2006) 2945-2955

- [17] B. G. Lee, A. V. Rylyakov, W. M. J. Green, S. Assefa, C. W. Baks, R. R.-Donadio, D. M. Kuchta, M. H. Khater, T. Barwicz, C. Reinholm, E. Kiewra, S. M. Shank, C. L. Schow, Y. A. Vlasov, Monolithic Silicon Integration of Scaled Photonic Switch Fabrics, CMOS Logic, and Device Driver Circuits, J. Lightw. Technol. 32(4) (2014) 743-351

- [18] C. Sun, M. T. Wade, Y. Lee, J. S. Orcutt, L. Alloatti, M. S. Georgas, A. S. Waterman, J. M. Shainline, R. R. Avizienis, S. Lin, B. R. Moss, R. Kumar, F. Pavanello, A. H. Atabaki, H. M. Cook, A. J. Ou, J. C. Leu, Y. H. Chen, K. Asanovi., R. J. Ram, M. A. Popovi, V. M. Stojanovi., Single-chip microprocessor that communicates directly using light, Nature 528 (2015) 534–538

- [19] I. Shubin, X. Zheng, H. Thacker, S. S. Djordjevic, S. Lin, P. Amberg, J. Yao, J. Lexau, E. Chang, F. Liu, N. Park, Microring-based multi-chip WDM photonic module, Opt. Express, 23(10), (2015) 13172-13184

- [20] K. W. Lee, A. Noriki, K. Kiyoyama, S. Kanno, R. Kobayashi, W. C. Jeong, J. C. Bea, T. Fukushima, T. Tanaka, M. Koyanagi, 3D Heterogeneous Opto-Electronic Integration Technology for System-on-Silicon (SOS), In IEEE International Electron Devices Meeting (IEDM) (2009) 1-4

- [21] A. Alduino, L. Liao, R. Jones, M. Morse, B. Kim, W.-Z. Lo, J. Basak, B. Koch, H.-F. Liu, H. Rong, M. Sysak, C. Krause, R. Saba, D. Lazar, L. Horwitz, R. Bar, S. Litski, A. Liu, K. Sullivan, O. Dosunmu, N. Na, T. Yin, F. Haubensack, I. Hsieh, J. Heck, R. Beatty, H. Park, J. Bovington, S. Lee, H. Nguyen, H. Au, K. Nguyen, P. Merani, M. Hakami, M. Paniccia, Demonstration of a High Speed 4-Channel Integrated Silicon Photonics WDM Link with Hybrid Silicon Lasers, Integrated Photonics Research, Silicon and Nanophotonics (2010)

- [22] S. Assefa, S. Shank, W. Green, M. Khater, E. Kiewra, C. Reinholm, S. Kamlapurkar, A. Rylyakov, C. Schow, F. Horst, H. Pan, T. Topuria, P. Rice, D. M. Gill, J. Rosenberg, T. Barwicz, M. Yang, J. Proesel, J. Hofrichter, B. Offrein, X. Gu, W. Haensch, J. E.-Monaghan, Y. Vlasov, A 90nm CMOS Integrated Nano-Photonics Technology for 25Gbps WDM Optical Communications Applications, Electron Devices Meeting (2012)

- [23] S. Tanaka, S. H. Jeong, S. Sekiguchi, T. Akiyama, T. Kurahashi, Y. Tanaka, K. Morito, Four-Wavelength Silicon Hybrid Laser Array with Ring-Resonator Based Mirror for Efficient CWDM Transmitter, Optical Fiber Communication Conference (2013) OTh1D-3

- [24] H. Ishii, N. Fujiwara, K. Watanabe, S. Kanazawa, M. Itoh, H. Takenouchi, Y. Miyamoto, Narrow Linewidth Operation (<10 kHz) in Self-injection-locked Tunable DFB Laser Array (SIL-TLA) Integrated with Optical Feedback Planar Lightwave Circuit (PLC), in proceedings of 42nd European Conference on Optical Communication (2016) 1-3</p>

- [25] J. Bovington, X. Zheng, S. Djordjevic, J. H. Lee, I. Shubin, Y. Luo, S. Lin, D. Lee, J. Yao, J. Cunningham, K. Raj, III-V/Si Tunable Vernier-Ring Flexible Grid Comb Laser, In CLEO: Science and Innovations (2016) JTh4C-2

- [26] B. Song, C. Stagarescu, S. Ristic, A. Behfar, J. Klamkin, 3D integrated hybrid silicon laser, Opt. Express 24(10) (2016) 10435-10444

- [27] R. E. Camacho-Aguilera, Y. Cai, N. Patel, J. T. Bessette, M. Romagnoli, L. C. Kimerling, J. Michel, An electrically pumped germanium laser, Opt. Express 20(10) (2012) 11316-11320

- [28] Z. Wang, B. Tian, M. Pantouvaki, W. Guo, P. Absil, J. V. Campenhout, C. Merckling, D. V. Thourhout, Room-temperature InP distributed feedback laser array directly grown on silicon, Nature Photon. 9 (2015) 837–842

- [29] A. Y. Liu, C. Zhang, J. Norman, A. Snyder, D. Lubyshev, J. M. Fastenau, A. W. K. Liu, A. C. Gossard, J. E. Bowers, High performance continuous wave 1.3 μm quantum dot lasers on silicon, Appl. Phys. Lett. 104(4) (2014) 041104

- [30] A. Lee, Q. Jiang, M. Tang, A. Seeds, H. Liu, Continuous-wave InAs/GaAs quantum-dot laser diodes monolithically grown on Si substrate with low threshold current densities, Opt. Express 20(20) (2012) 22181-22187

- [31] S. Chen, W. Li, J. Wu, Q. Jiang, M. Tang, S. Shutts, S. N. Elliott, A. Sobiesierski, A. J. Seeds, I. Ross, P. M. Smowton, H. Liu, Electrically pumped continuous-wave III–V quantum dot lasers on silicon, Nat. Photon. 10 (2016) 307-311

- [32] A. W. Fang, H. Park, O. Cohen, R. Jones, M. J. Paniccia, J. E. Bowers, Electrically pumped hybrid AlGaInAs-silicon evanescent laser, Opt. Express 14(20) (2006) 9203-9210

- [33] D. Liang, J. E. Bowers, Recent progress in lasers on silicon, Nat. Photon. 4 (8) (2010) 511-517

- [34] M. J. R. Heck, J. F. Bauters, M. L. Davenport, J. K. Doylend, S. Jain, G. Kurczveil, S. Srinivasan, Y. Tang, J. E. Bowers, Hybrid silicon photonic integrated circuit technology, IEEE J. Quantum Electron. 19(4) (2013) 6100117

- [35] T. Komljenovic, M. Davenport, J. Hulme, A. Liu, C. Santis, A. Spott, S. Srinivasan, E. Stanton, C. Zhang, J. Bowers, Heterogeneous silicon photonic integrated circuits, J. Lightwave Technol. 34(1) (2015) 20-35

- [36] X. Luo, Y. Cao, J. Song, X. Hu, Y. Cheng, C. Li, C. Liu, T.-Y. Liow, M. Yu, H. Wang, Q. J. Wang, P. G.-Q. Lo, High-throughput multiple dies-to-wafer bonding technology and III/V-on-Si hybrid lasers for heterogeneous integration of optoelectronic integrated circuits, Front. Mater. 2(28) (2015) 1-21

- [37] S. R. Jain, Y. Tang, H.-W. Chen, M. N. Sysak, J. E. Bowers, Integrated Hybrid Silicon Transmitter, J. Lightwave Technol. 30(5) (2013) 671-678

- [38] H. Park, M. N. Sysak, H.-W. Chen, A. W. Fang, D. Liang, L. Liao, B. R. Koch, J. Bovington, Y. Tang, K. Wong, M. J.-Mitos, R. Jones, J. E. Bowers, Device and Integration Technology for Silicon Photonic Transmitters, IEEE J. Quantum Electron. 17(3) (2011) 671 - 688

- [39] D. Huang, P. Pintus, C. Zhang, Y. Shoji, T. Mizumoto, J. E. Bowers, Electrically Driven and Thermally Tunable Integrated Optical Isolators for Silicon Photonics, IEEE J. Sel. Top. Quantum Electron. 22(6) (2016) 4403408

- [40] A. Spott, E. J. Stanton, N. Volet, J. D. Peters, R. J. Meyer, J. E. Bowers, Heterogeneous Integration for Mid-Infrared Silicon Photonics, IEEE J. Sel. Top. Quantum Electron. PP(99) (2017) 1

- [41] L. Chang, Y. Li, N. Volet, L. Wang, J. Peters, J. E. Bowers, Thin film wavelength converters for photonic integrated circuits, Optica 3(5) (2016) 531-535

- [42] G. Kurczveil, D. Liang, M. Fiorentino, R. G. Beausoleil, Robust hybrid quantum dot laser for integrated silicon photonics, Opt. Express 24(14) (2016) 16167-16174

- [43] J. Sun, E. Timurdogan, A. Yaacobi, E. S. Hosseini, M. R. Watts, Large-scale nanophotonic phased array, Nature 493 (2013) 195-199

- [44] C. Zhang, S. Zhang, J. D. Peters, J. E. Bowers, 8 × 8 × 40 Gbps Fully-Integrated Silicon Photonic Network-on-Chip, Optica 3 (7) (2016) 785-786

- [45] D. Vantrease, R. Schreiber, M. Monchiero, M. McLaren, N. P. Jouppi, M. Fiorentino, A. Davis, N. Binkert, R. G. Beausoleil, J. H. Ahn, "Corona: System implications of emerging nanophotonic technology, Int. Symp. Computer Architecture, (2008) 153–164.

- [46] Y. Pan, P. Kumar, J. Kim, G. Memik, Y. Zhang, A. Choudhary, Firefly: Illuminating future network-on-chip with nanophotonics, 36th Annu. Int. Symp. Computer Architecture, (2009) 429–440.

- [47] G. Kurian, J. E. Miller, J. Psota, J. Eastep, J. Liu, J. Michel, L. C. Kimerling, A. Agarwal, ATAC: A 1000-core cachecoherent processor with on-chip optical network. 19th Int. Conf. Parallel Architectures and Compilation Techniques. (2010) 477–488.

- [48] S. L. Beux, H. Li, I. O'Connor, K. Cheshmi, X. Liu, J. Trajkovic, G. Nicolescu, Chameleon: Channel efficient optical network-on-chip, Proceedings of the conference on Design, Automation & Test in Europe, (2014) 34

- [49] Y. Ye, J. Xu, B. Huang, X. Wu, W. Zhang, X. Wang, M. Nikdast, Z. Wang, W. Liu, Z. Wang, 3-D Mesh-Based Optical Network-on-Chip for Multiprocessor System-on-Chip, IEEE Trans. Comput. -Aided Design Integr. Circuits Syst. 32(4) (2013) 584-596

- [50] C. Zhang, S. Srinivasan, Y. Tang, M. J. R. Heck, M. L. Davenport, J. E. Bowers, Low threshold and high speed short cavity distributed feedback hybrid silicon lasers, Opt. Express 22(9) (2014) 10202-10209

- [51] S. Srinivasan, A. W. Fang, D. Liang, J. Peters, B. Kaye, J. E. Bowers, Design of phase-shifted hybrid silicon distributed feedback lasers, Opt. Express 19(10) (2011) 9255-9261

- [52] Y. Tang, J. D. Peters, J. E. Bowers, Energy Efficient Hybrid Silicon Electroabsorption Modulator for 40 Gb/s, 1-Volt Uncooled Operation, IEEE Photon. Technol. Lett 24(19) (2012) 1689-1692

- [53] Y.-H. Kuo, H.-W. Chen, J. E. Bowers, High speed hybrid silicon evanescent electroabsorption modulator, Opt. Express, 16(13) (2008) 9936-9941

- [54] H.-W. Chen, J. D. Peters, J. E. Bowers, Forty Gb/s hybrid silicon Mach-Zehnder modulator with low chirp, Opt. Express 19(2) (2011) 1455-1460

- [55] H. Park, A.W. Fang, R. Jones, O. Cohen, O. Raday, M. N. Sysak, M. J. Paniccia, J. E. Bowers, A hybrid AlGaInAs-silicon evanescent waveguide photodetector, Opt. Express 15(10) (2007) 6044-6052

- [56] X. Ma, G. S. Kuo, Optical switching technology comparison: optical MEMS vs. other technologies, IEEE Commun. Mag. 41(11) (2003) S16-S23

- [57] P. Dong, S. F. Preble, M. Lipson, All-optical compact silicon comb switch, Opt. Express 15(15) (2007) 9600-9605

- [58] P. Pintus, P. Contu, N. Andriolli, A. D'Errico, F. Di Pasquale, F. Testa, Analysis and design of microring-based switching elements in a silicon photonic integrated transponder aggregator, J. Lightw. Technol. 31(24) (2013) 3943-3955

- [59] S. L. Tsao, H. C. Guo, Y. J. Chen, Design of a 2×2 MMI MZI SOI electro-optic switch covering C band and L band, Microw. Opt Technol. Lett. 33(4) (2002) 262-265

- [60] J. Van Campenhout, W. M. J. Green, S. Assefa, Y. A. Vlasov, Low-power, 2×2 silicon electro-optic switch with 110-nm bandwidth for broadband reconfigurable optical networks, Opt. Express 17(26) (2009) 24020-24029

- [61] R. Adar, C. H. Henry, R. F. Kazarinov, R. C. Kistler, G. R. Weber, AC Adiabatic 3-dB couplers, filters and multiplexers made with silica waveguides on silicon, J. Lightw. Technol. 10(1) (1992) 46-50

- [62] M. A. Tran, C. Zhang, J. E. Bowers, A broadband optical switch based on adiabatic couplers, IEEE Photonics Conference (2016)

- [63] D. Dai, L. Liu, L. Wosinski, S He, Design and fabrication of ultra-small overlapped AWG demultiplexer based on-Si nanowire waveguides, Electron. Lett. 42(7) (2006) 400-402

- [64] M. Piels, J. F. Bauters, M. L. Davenport, M. J. R. Heck, J. E. Bowers, Low-loss silicon nitride AWG demultiplexer heterogeneously integrated with hybrid III–V/silicon photodetectors, J. Lightw. Technol. 32(4) (2014) 817-823

- [65] M. K. Smit, C. Van Dam, PHASAR-based WDM-devices: Principles, design and applications, IEEE J. Sel. Top. Quantum Electron. (1996) 2 (2)

- [66] F. Ohno, K. Sasaki, A. Motegi, T. Baba, Reduction in sidelobe level in ultracompact arrayed waveguide grating demultiplexer based on Si wire waveguide, Jpn. J. Appl. Phys. 45(8A) (2006) 6126-6131

- [67] T. Ye, Y. Fu, L. Qiao, T. Chu, Low-crosstalk Si arrayed waveguide grating with parabolic tapers, Opt. Express 22(26) (2014) 31899-31906

- [68] H. Fukano, Y. Akage, Y. Kawaguchi, Y. Suzaki, K. Kishi, T. Yamanaka, Y. Kondo, H. Yasaka, Low chirp operation of 40 Gbit/s electroabsorption modulator integrated DFB laser module with low driving voltage, IEEE J. Sel. Top. Quant. Electron. 13(5) (2007) 1129–1134

- [69] W. Kobayashi, M. Arai, T. Yamanaka, N. Fujiwara, T. Fujisawa, T. Tadokoro, K. Tsuzuki, Y. Kondo, F. Kano, Design and fabrication of 10-/40-Gb/s, uncooled electroabsorption modulator integrated DFB laser with butt-joint structure, J. Lightwave Technol. 28(1) (2010) 164–171

- [70] C. Sun, B. Xiong, J Wang, P Cai, J. Xu, J. Huang, H. Yuan, Q. Zhou, Y. Luo, Fabrication and packaging of 40-Gb/s AlGaInAs multiple-quantumwell electroabsorption modulated lasers based on identical epitaxial layer scheme, J. Lightwave Technol. 26(11) (2008) 1464–1471

- [71] G. Kurczveil, D. Liang, M. Fiorentino, R. G. Beausoleil, A compact, high-speed, highly efficient hybrid silicon photodetector, IEEE Optical Interconnects Conference (2016) 98-99

- [72] J. Bowers, C. Burrus, Ultrawide-band long-wavelength pin photodetectors, J. Lightw. Technol. 5(10) (1987) 1339-1350

- [73] F. Van Laere, G. Roelkens, M. Ayre, J. Schrauwen, D. Taillaert, D. Van Thourhout, T. F. Krauss, R. Baets, Compact and Highly Efficient Grating Couplers Between Optical Fiber and Nanophotonic Waveguides, J. Lightw. Technol. 25(1) (2007) 151-156

- [74] C. Li, H. Zhang, M. Yu, G. Q. Lo, CMOS-compatible high efficiency double-etched apodized waveguide grating coupler, Opt. Express 21(7) (2013) 7868-7874

- [75] N Hatori, T Shimizu, M Okano, M. Ishizaka, T. Yamamoto, Y. Urino, M. Mori, T. Nakamura, Y. Arakawa, A Novel Spot Size Convertor for Hybrid Integrated Light Sources on Photonics-Electronics Convergence System, The 9th International Conference on Group IV Photonics (GFP) (2012) 171-173

- [76] L. Chen, C. R. Doerr, Y. K. Chen, T. Y. Liow, Low-Loss and Broadband Cantilever Couplers Between Standard Cleaved Fibers and High-Index-Contrast Si N or Si Waveguides, IEEE Photon. Technol. Lett. 22(23) (2010) 1744-1746

- [77] V. R. Almeida, R. R. Panepucci, M. Lipson, Nanotaper for compact mode conversion, Opt. Lett. 28(15) (2003) 1302-1304

- [78] M. Bahadori, D. Nikolova, S. Rumley, C. P. Chen, K. Bergman, Optimization of Microring-based Filters for Dense WDM Silicon Photonic Interconnects, IEEE Optical Interconnection Conference TuP12, 201

- [79] D. Liang, X. Huang, G. Kurczveil, M. Fiorentino, R. G. Beausoleil, Integrated finely tunable microring laser on silicon, Nature Photonics, 10(11) (2016) 719-722